| 送交者: 千牛卫[★★无眠的人★★] 于 2020-09-01 17:54 已读 976 次 1 赞 | 千牛卫的个人频道 |

6park.com

NVIDIA的新一代Ampere架构随最新的计算卡A100正式亮相,这张加速卡上面使用的GA100核心也是目前世界上最大的7nm核心,其面积高达826mm2。那么这枚核心中包含的Ampere架构与前代相比究竟在哪些地方有不同呢?本文就带各位一起简单地看看这个NVIDIA最新一代图形架构。首先我们的旅程从整个GA100 GPU开始,下图是官方提供的GA100 GPU全貌(可以点击打开原图)。

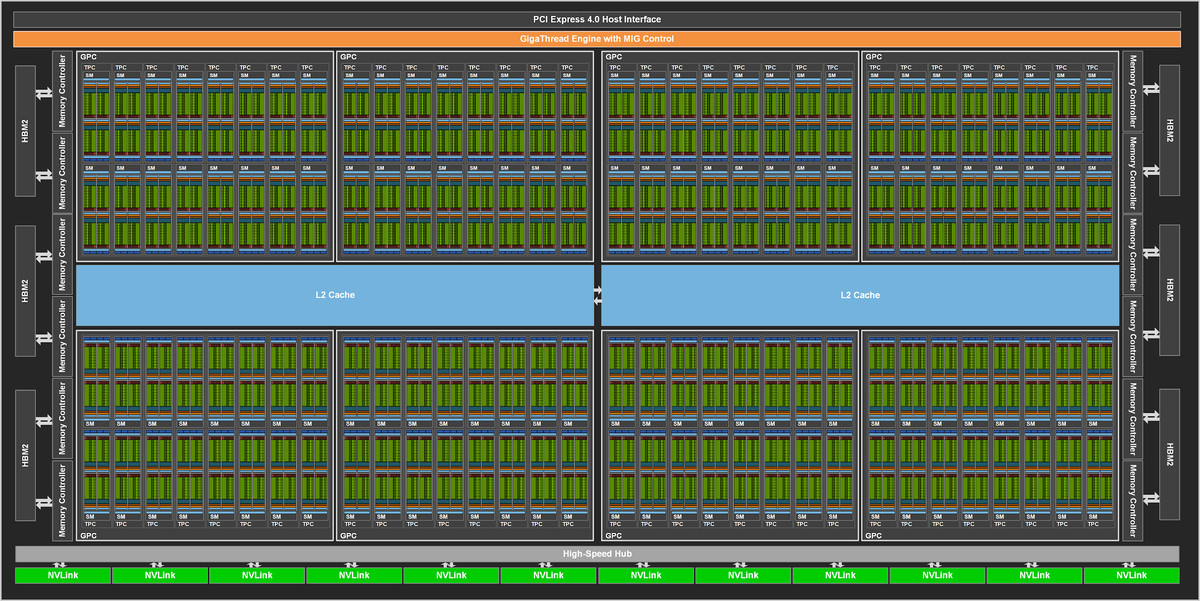

分割成了两组的超大L2缓存和超高显存带宽Ampere架构仍然沿用了成熟的GPC-TPC-SM多级架构,GA100内部包含8组GPC,每组GPC包含8组TPC,每组TPC又包含8组SM。主要的区别点在于,中间的L2缓存不再是统一的一组,而是被分割成了两组。实际上,GA100的L2缓存相比起前代的GV100要大上近7倍——从原本的6MB直接跳到了40MB。大容量的L2缓存会在一定程度上减轻计算单元对显存带宽的依赖,不过为了避免访问远端L2缓存时出现延迟过高的问题,它被分成了两块,保证延迟不过高。这种大容量特性和分割结构让GA100的L2缓存带宽提升了2.3倍,同时硬件的缓存一致性保证应用程序可以自动利用大容量的L2缓存提升性能。 6park.com

NVIDIA三代顶级计算卡规格对比表

Tesla P100Tesla V100A100GPC668TPC284054SM5680108FP32/SM646464FP32/GPU358451206912FP64/SM323232FP64/GPU179225603456Tensor Cores代数N/A第一代第三代Tesor Cores/SMN/A84材质单元224320432显存接口4096-bit HBM24096-bit HBM25120-bit HBM2 ECC显存容量16 GB32/16 GB40 GB显存带宽720 GB/s900 GB/s1555 GB/s二级缓存大小4 MB6 MB40 MBSM单元共享缓存大小64 KB96 KB164 KB寄存器文件大小/SM256 KB256 KB256 KB寄存器文件大小/GPU14 MB20 MB27 MBTDP300 W300 W400 W芯片面积610 mm2815 mm2826 mm2制程工艺16nm FinFET+12nm FFN7nm N7超 能 网 制 作 6park.com除了容量和结构上的变化,Ampere也在架构上引入了名为计算数据压缩(Compute Data Compression)的新缓存特性,它可以加速非结构化的稀疏数据和其他可压缩的数据,使DRAM的读写带宽能够提升4倍,L2中的读取带宽提升4倍,容量提升2倍。同时,针对大容量的L2缓存,Ampere为程序员提供了数据驻留控制,允许用户对缓存数据进行管理,可以手动将一些数据保留在L2中,加速持久化的访问。

另外在显存带宽上面,A100也有突破。它仍然使用了HBM2的显存,一共五个活动堆栈,每个堆栈中有8片8Gb显存,最终组成40GB的显存,运行在1215MHz的频率上,其显存带宽高达1555GB/s,是V100的1.7倍多。另外它具备ECC硬件校验功能,需要占用额外的显存,这也就是在架构图和渲染图上,GA100均拥有6组HBM2显存,而只有5组是实际可用的原因了。而且不仅仅是显存,GPU内部的所有寄存器、L1和L2缓存均支持ECC特性。

新的数据接口再来看上下的外围部分,首先比较显眼的应该是PCI Express 4.0。相信我们的读者对PCIe 4.0已经很熟悉了,这里也就不讲具体的了,只要知道它的带宽比3.0提升了一倍即可。

在NVIDIA的计算阵列中用的更多的是NVLink这个专门用来让GPU实现互联的接口,在Ampere上,NVLink升级到了第三代。第三代NVLink将每个信号对(signal pair)的数据速率提升到了50Gb/s,比前代几乎提升一倍,单个第三代NVLink在每个方向上面能够提供25GB/s的带宽,这与上代类似,但少用了一半的信号对,这也使得GA100上面的NVLink链路总数直接扩增了一倍,达到12条,总带宽达到600GB/s,比GV100提升一倍。

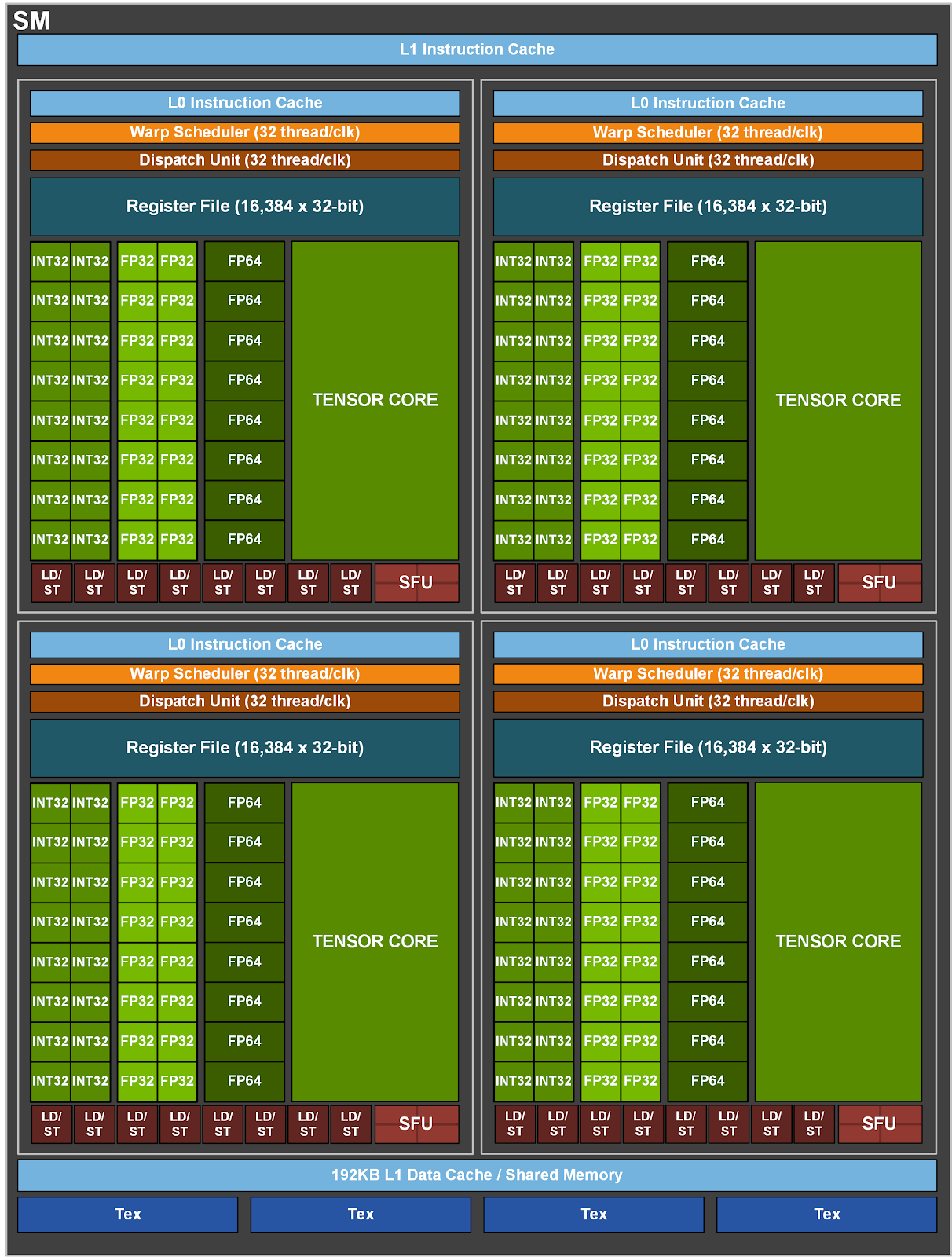

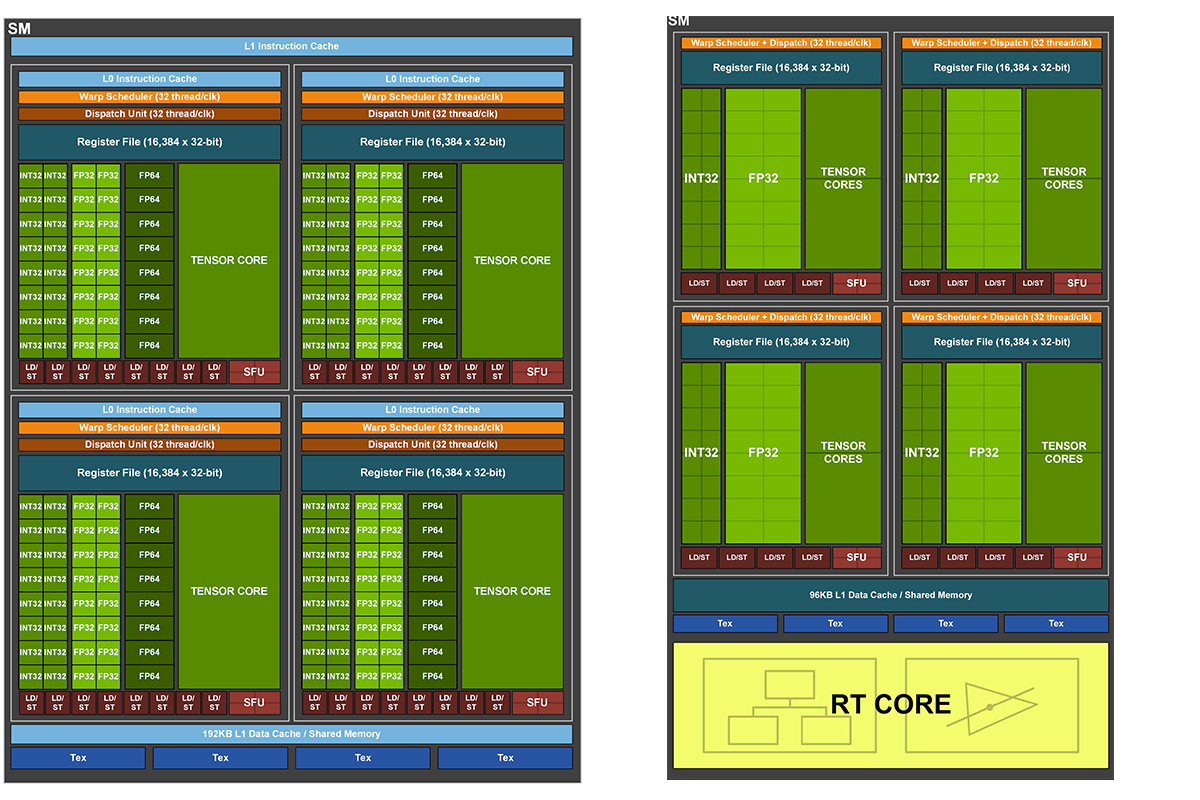

延续Volta的SM设计看完更新了的数据交换接口,让我们把这张图放到放大镜下面,来看一看Ampere,应该说是GA100的SM单元设计。

GA100的SM单元如果要搞明白它的变化点,我们还要请出Volta架构和Turing架构的SM单元。

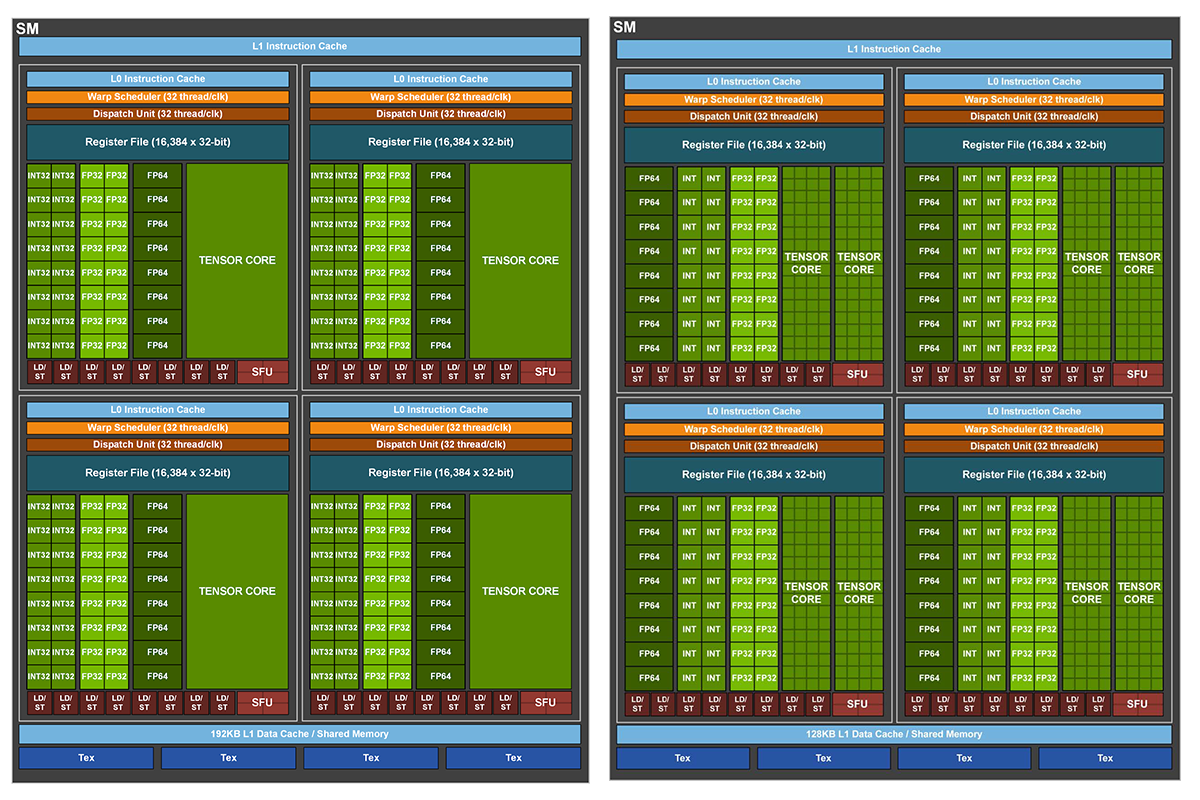

左GA100,右GV100

左GA100,右TU102可以看到Ampere的SM单元设计保留了从Volta开始的分精度计算思路,将计算核心分成了针对整数计算的INT32单元和针对浮点计算的FP32、FP64单元和针对FP16、INT8等AI计算中常见的数据类型的Tensor Cores。从数量来看,每个SM仍然拥有64个FP32单元、64个INT32单元和32个FP64单元,这与Volta和Turing没有太大的区别(Turing SM没有FP64单元)。比较明显的区别在于,在Ampere SM中,每SM仅包含四个Tensor Core。至于RT Cores?那是游戏卡才有的,面对纯计算用途的GA100自然不需要这玩意儿。

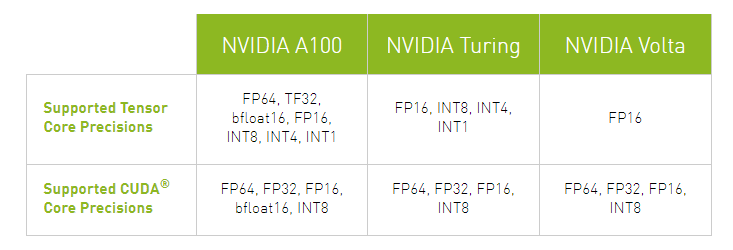

大幅加强的Tensor Cores是的,Tensor Cores变少了,但是它变强了。在Ampere架构上,Tensor Cores升级到了第三代,这也是Ampere SM中变化最大的地方了。第三代Tensor Cores变得几乎无所不能,它可以加速几乎所有的常见数据类型,包括FP16、BF16、TF32、FP64、INT8、INT4和二进制。下面是官方的代际数据类型对比表:

不仅仅是支持的数据类型变多了,它的算力也有很大的提高,现在每个Tensor Cores在每个时钟内可以执行256次FP16/FP32 FMA操作,在前代,这个数字是64次。也就是提高了足足4倍,于是,就算是每个SM中减少一半的Tensor Cores,它仍然能够提供两倍于前代的性能。

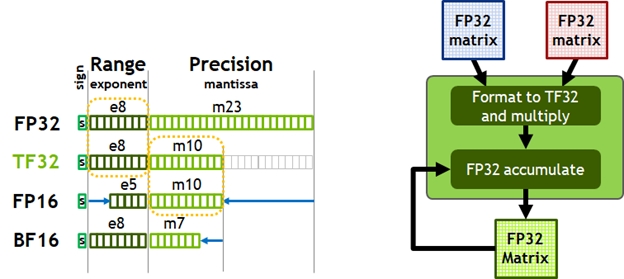

另外,为了提高Tensor Cores训练AI时的效率,NVIDIA新创了一种名为TF32的数据类型,它拥有FP32的范围和FP16的精度,对于调用Tensor Core的操作,它会自动启用TF32进行处理。而没有调用Tensor Cores的操作将仍然走FP32的数据路径,Tensor Cores会自动读取FP32数据,在内部减精度进行运算,在最终输出的时候会将数据还原成IEEE标准。

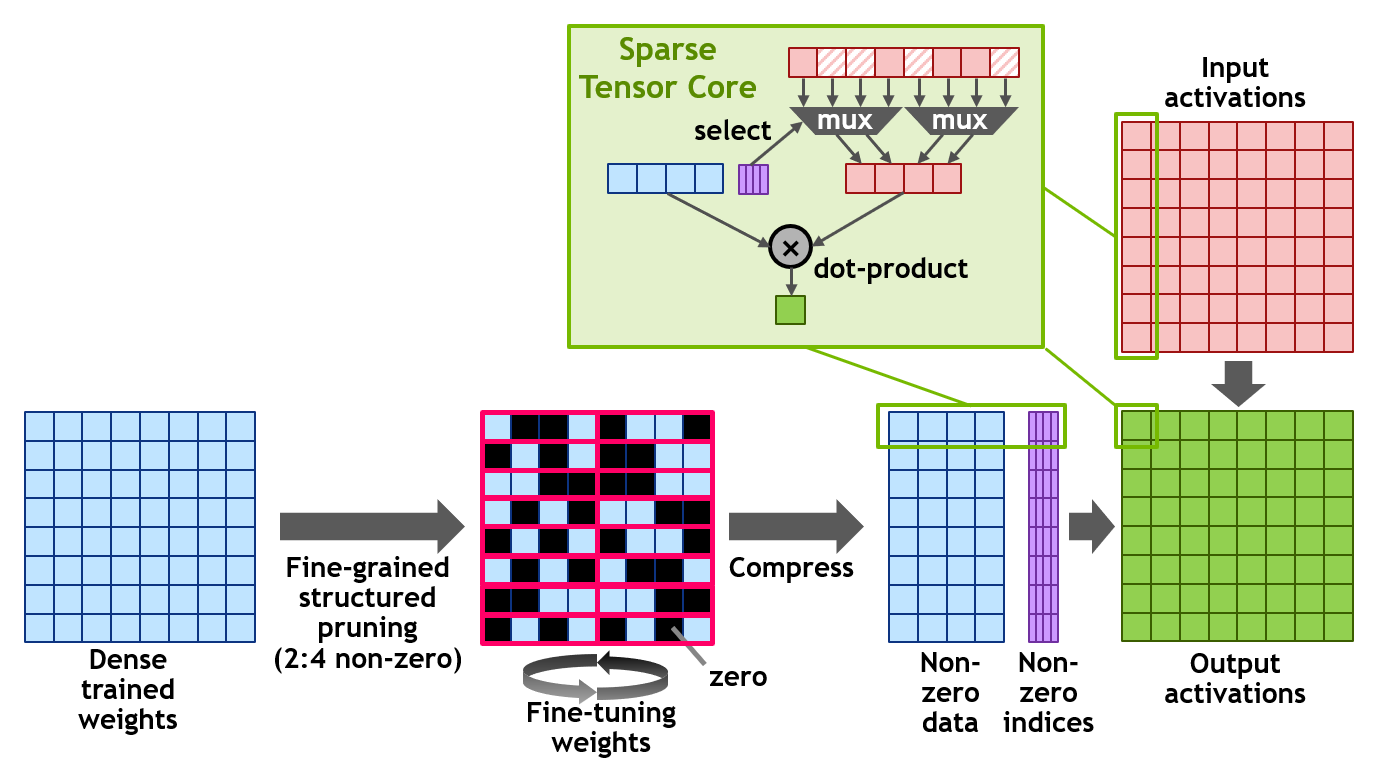

新版Tensor Cores还支持稀疏矩阵运算。稀疏矩阵指的是大部分元素为0的矩阵,对于这种矩阵,NVIDIA使用了自己开发出来的稀疏计算方式,它支持2:4的结构化稀疏运算,需要参与计算的矩阵在每四个元素中有2个以上的0元素,它可以将Tensor Cores的计算吞吐量翻一倍。

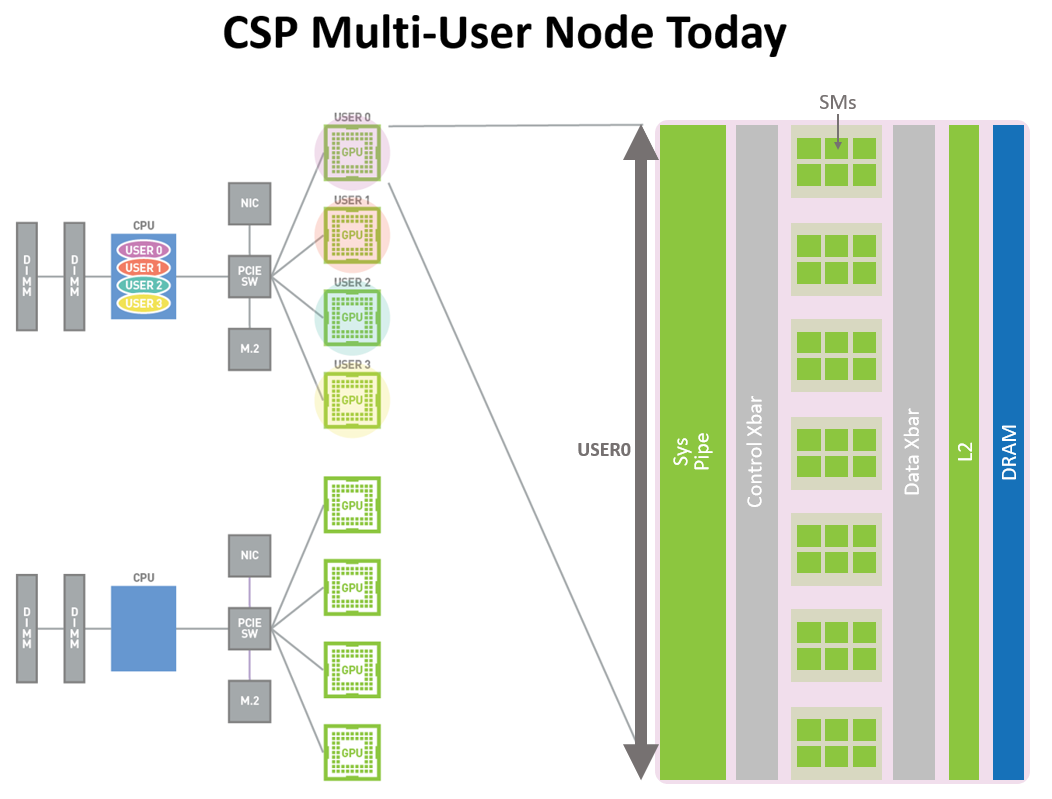

虚拟多实例(MIG)特性数据中心多采用虚拟化技术为客户提供计算实例,在CPU虚拟化上面,现有的方案已经非常成熟,但对于GPU,现有的虚拟化方案就不太能够满足当前数据中心的需求,如同下图中所示意的,一个CPU可能会被多名用户同时占用,而一块GPU在单一时间内只能被一名用户所使用,这就有可能造成资源浪费。设想一下,用户1只需要0.5块GPU的资源即可完成任务,而用户2则需要1.5块GPU资料,如果按照CPU虚拟化的方式,那么此时2块GPU即可满足用户的需求,但因为GPU并不能够分块,使得数据中心要给用户分配1+2共3块GPU,才能够满足需求,这无疑是浪费了计算资源。

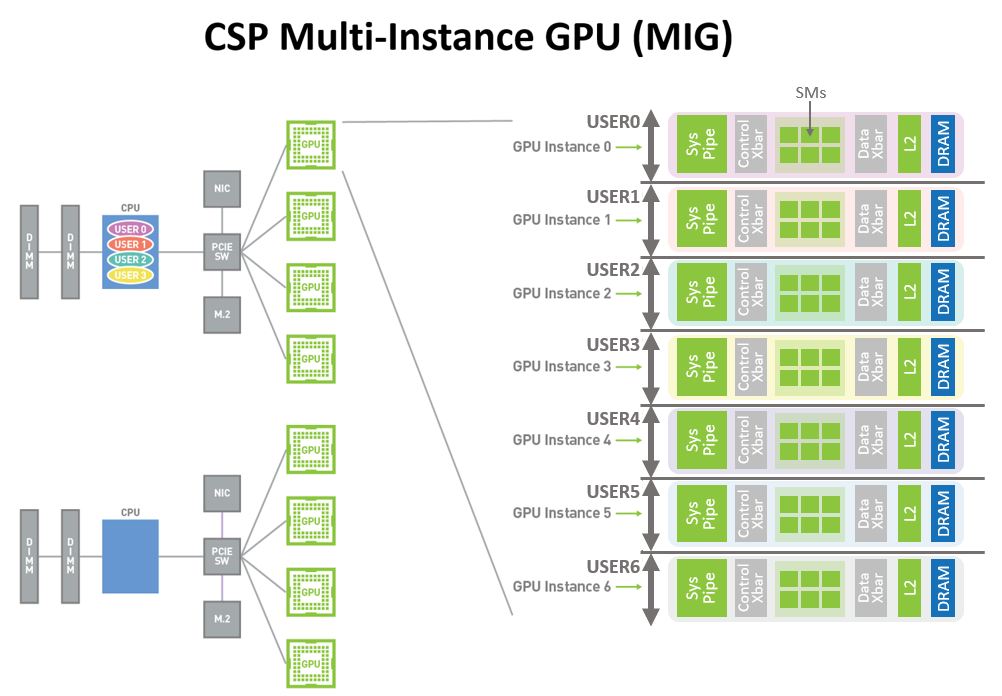

而Ampere上面引入的多实例GPU(Multi-Instance GPU)特性则很好地从硬件上面解决了当前数据中心在GPU资源分配上面遇到的问题,它在硬件底层即可将整块显卡切分成7个独立实例,并且可以分配给不同用户使用。

MIG特性的引入实际上是将GPU资源进行了细粒度的划分,就有如CPU按核心数量来划分计算资源一样,不过GPU暂时还做不到细化到单个SM单元这么细,但已经是为虚拟化做出了重大的升级。

总结:改良性的更新,让人更期待游戏版的改变总的来说,Ampere架构的更新并不是革命性的,而是延续了NVIDIA这几年在架构设计上的一贯思路,微观上在SM单元中延续分精度计算,并加强Tensor Cores这个对深度学习计算非常有用的单元,宏观上面增大GPU的规模,不仅将整个GPU包含的SM单元数量扩大到128组这个数字,更是把整片GPU上面的缓存系统都放大了,尤其是40MB的二级缓存,让人印象深刻。

不过,GA100是一个为计算而特别设计的核心,虽然Ampere将会同时登陆计算卡和图形卡之中,但它们的配置会有一些不同。我们目前可以判断的是,Ampere的图形版中势必会取消掉所有FP64单元,另外Turing中引入的RT Cores将会被继承,Tensor Cores也应该会升级到第三代。而其他改动,像是SM的共享缓存大小和寄存器文件大小,应该会被保留,但二级缓存应该不会有40MB那么夸张了,另外,显存接口肯定会改到更为便宜的GDDR6上去。至于核心的规模嘛……肯定不会比GA100大(废话),但这代在CUDA Core上貌似没有进行太大的改进,如果想要在图形性能上进行提升,那要么是提升频率,要么是扩大规模,两者并行下来,未来的GA102芯片在FP32的数量上面可能会逼近A100计算卡的6912个,当然,拿到GeForce中肯定会挨上几刀。

那么,关于Ampere架构的简要解读就到此为止了,对于我们来说,更有用的内容还是要等到图形卡出来才有的分析。本文主要参考了官方的《NVIDIA Ampere Architecture In-Depth》,由于本人能力和认知有限,文章中难免会有错误,还请各位读者指出。